# Department of Higher Education University of Computer Studies, Yangon

## Third Year (B.C.Tech.) Final Examination

## Computer Architecture I (CT 305)

### October, 2018

### Answer all questions.

Time allowed: 3 hours

- 1(a) Describe the limitations of computers and important speedup techniques of modern computers.

(10 marks)

- (b) The performance of a 100 MHz microprocessor *P* is measured by executing 10, 000, 000 instructions of benchmark code, which is found to take 0.25s. What are the values of *CPI* and *MIPS* for this performance experiment? Is *P* likely to be superscalar? (10 marks)

- 2(a) Design a two-level combinational circuit in the sum-of-products style that computes the 3-bit sum of two 2-bit binary numbers. The circuit is to be implemented using AND and OR gates.

(10 marks)

- (b) Design an edge-triggered D flip-flop by using Actel FPGA C-Modules as shown in Figure 1. And then also construct an Actel FPGA S-Module from this C-Module. (10 marks)

Figure 1. Actel ACT-series FPGA(basic cell C-Module)

3(a) Consider the instruction mixes appearing in the following table. Suppose that the system's clock frequency is 100MHz, and all instructions except floating-point instructions have average execution times of 10ns. (i) What is the average execution time of floating-point instructions, if the overall average execution time per instruction for program B is 18.1 ns? (ii) What is the CPI for program B?

| Instruction Type      | Probability of occurrence |                        |

|-----------------------|---------------------------|------------------------|

|                       | Program A (Commercial)    | Program B (Scientific) |

| Memory Load           | 0.24                      | 0.29                   |

| Memory Store          | 0.12                      | 0.15                   |

| Fixed-point operation | 0.27                      | 0.15                   |

Page 1 of 2

| Floating-point operations | 0.00 | 0.19 |

|---------------------------|------|------|

| Branch                    | 0.17 | 0.10 |

| Other                     | 0.20 | 0.12 |

(b) Suppose that CPU behavior in a multiprogramming system can be analyzed using the M/M/1 queueing model. Programs are sent to the CPU for execution at a mean rate of eight programs per minute and are executed on a first-come first-served basis. The average program requires six seconds of CPU execution time. (i) What is the mean time between program arrivals at the CPU? (ii) What is the mean number of programs waiting for CPU execution to be completed? (iii) What is the mean time a program must wait for its execution to be completed?

(10 marks)

4(a) Write the shortest ARM6 program that can to implement the following conditional statement: while  $(x \neq y)$  do x := y - 1;

Assume that x and y are stored in CPU registers R1 and R2, respectively. (10 marks)

- (b) Write the vector addition program written in 680X0 assembly-language code to compute the sum C:= A+B for adding two 1000-element vectors A and B to produce a third vector C. Vector A is stored in memory location 1001, 1002,..., 1999, 2000; vector B is stored in memory location 2001, 2002,..., 2999, 3000; and vector C is also stored in memory location 3001, 3002,..., 3999, 4000. (10 marks)

- 5(a) (i) Derive the correct floating point representation for the decimal number +3.5 using the 32-bit IEEE 754 floating-point standard.

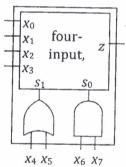

- (b) Suppose the memory data register DR in a CPU transfers 32-bit words to M in a single clock cycle. The data item D to be stored may be 16 or 32 bits long. If a 16-bit data item D is placed in DR, it is automatically extended to 32 bits as it is transmitted from DR to M. The size of D is given by a flag S, whose 0 and 1 values denote 16 and 32 bits, respectively. The extension method is given by a second flag E, whose 0 and 1 values denote zero extension and sign extension, respectively. Design a register-level logic circuit to perform the needed extension, making it as simple and as fast as possible.

(10 marks)